1.引言

软件定义网络(SDN)采用控制与转发分离结构,由于允许网络拥有者和运营商对网络行为进行编程而取得巨大的成功,在工业界得到广泛认可。各种开源项目,如ODL和ONOS等,在SDN技术发展中扮演重要角色,是推动SDN应用的最大动力。

可编程交换是当前SDN的研究热点之一。如何实现高性能的openflow流表查表,如何扩展SDN交换平面功能,如何实现对高级语言编程(P4)的支持等在学术界都得到了广泛研究。然而与目前存在的大量开源SDN控制器不同,开源SDN交换机难以满足SDN科研与教学的需要。OpenVSwitch功能全面,但全软件的实现方式难以满足高性能处理需求;NetFPGA实现了openflow 1.0交换,但近年来很难看到后续的发展;国内南京叠锶的ONetSwitch在FPGA上实现了完善的SDN交换功能,但交换机采用FPGA内嵌的处理器,能力较弱,难以在处理器上进行数据路径处理功能的扩展。

2011年开始,国防科技大学、北京邮电大学和东南大学等单位相关的课题组基于可编程交换平台NetMagic08进行了SDN实验平台的开发,形成了支持openflow1.0/1.3的SDN交换机。并采用多核CPU+FPGA的架构(Netmagic Pro平台),实现了支持SDN数据平面功能扩展的Labelcast交换机以及软件定义隧道交换机(SDTS)等成果。2016年,课题组基于上述成果形成FAST(Fpga bAsed Sdn swiTch)开源项目,支持国内SDN交换技术的创新研究和相关的教学工作。

2. 科研与教学对开源SDN交换机的需求

与在工业界应用不同,面向科研与教学领域的开源项目的目标用户主要是研究机构和大学中参与SDN技术研究的老师和研究生,这些人员在网络知识储备、编程水平、有意投入工程实现的时间等方面具有较大差异,因此对开源SDN交换项目也有不同的需求,主要具有以下特点。

(1)内部交换机内部的实现流程可见

研究人员、老师和学生可以看到交换机内部详细的工作流程,包括硬件对报文的处理波形,交换机内部软硬件交互的流程,以及交换机通过南向接口与控制器的通信流程。目前的市场采购的SDN交换机无法看到内部工作流程,对研究人员来说是一个典型的“黑盒”,只能通过各种配置命令改变交换机的处理行为,或在开源的控制器一侧通过抓包软件观测交换机的外部行为,对SDN交换技术的研究支持不足。

(2)能够在交换机中增加自己的创新工作

SDN的创新研究有可能需要增加一个定制的模块来修改硬件处理逻辑,如支持新的分组格式,新的调度算法,也有可能是通过在硬件逻辑中(或者流表中)设置一个“钩子”,将指定的流量定向到CPU,通过编写软件代码实现对特定流量施加特定处理。目前基于ASIC的商用SDN交换机难以支持上述功能,新型可编程SDN芯片(如Barefoot支持P4的芯片)尚未成熟,而且也是无法在硬件处理层次的创新实验。

(3)需要更好的应用和开发支持

由于在教学科研领域的研究人员,特别是研究生,水平层次不齐。特别电子工程专业的可能擅长硬件设计,计算机专业的可能擅长软件编程,以论文为目标的研究人员可能更加注重原理的验证而不是工作的稳定性,而部分科研院所希望能够稳定可靠的工作,成为产品的原型。因此研究人员希望能够获得更加专业,甚至是定制的服务。

(4)平台中立,不涉及具体的商业利益

科研教学领域的研究主要是面向关键技术的突破和验证,以及SDN原理的学习。基本不涉及到各种商业利益的纷争,因此平台应该具有中立性,不能依赖特定的平台和操作系统,也不能与其他特定的开源项目绑定发展。

因此,100G/40G高速接口和几十甚至是上百个的端口密度不是科研与教学平台的第一需求,内部处理流程可见,平台处理功能可定制,良好的服务技术支持,以及不带有商业倾向性的平台设计才是科研教学领域的最重要需求。

3.FAST的技术路线

3.1 FAST硬件架构

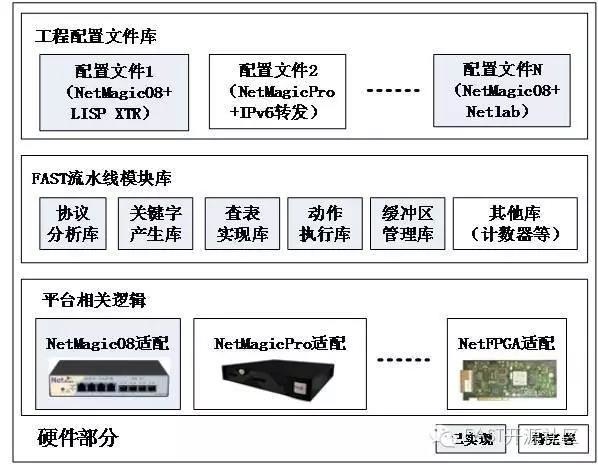

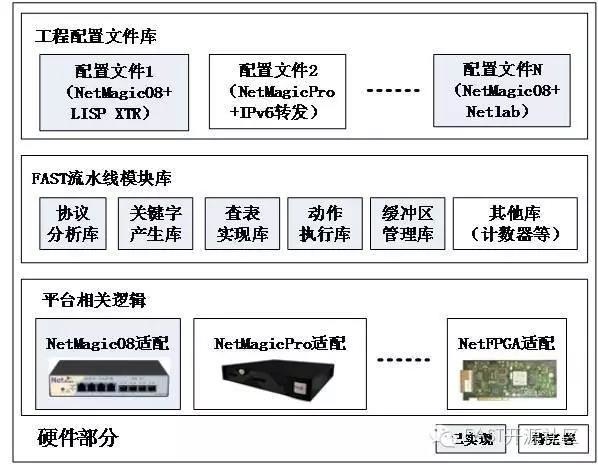

FAST的FPGA设计主要分为平台相关逻辑、FAST流水线模块库以及工程配置文件库三部分,如图1所示。平台相关逻辑主要是各类用于网络实验的FPGA平台,如NetMagic08,NetMagic Pro以及NetFPGA等为了支持FAST交换机需要提供的基本功能,包括物理网络接口分组的收发,与CPU的通信,访问板卡外围协处理器(如TCAM)和存储器的接口等。

FAST流水线模块库包含了实现SDN交换逻辑的主要功能模块,这些模块是在前期项目开发中积累的,包括协议分析,关键字提取、查表,动作(封头/去头,令牌桶限速等)、缓冲区管理和计数器等模块。用户可根据这些模块,针对自己的需求搭建自己的SDN转发流水线。

工程配置文件库类似C语言的makefile文件,用户可使用工程配置文件指定FPGA选用的平台,将平台相关逻辑以及FAST流水线多个模块组成一个工程。由于在FAST流水线模块设计中依赖一些器件相关的宏(如基于Altera Quartus II工具生成的FIFO、PLL等实例),因此目前工程配置库只支持基于Altera FPGA的可编程板卡。

FAST UM规范定义了平台相关逻辑与FAST交换逻辑的接口,详细见《FAST UM接口规范》。基于FAST UM规范设计的SDN转发逻辑可以方便的在不同的,支持FSAT 的FPGA平台上移植。例如SDN转发逻辑可以在相对简单的NetMagic08平台上调试,完成后再移植到NetMagic Pro平台。

图1 FAST项目的硬件架构

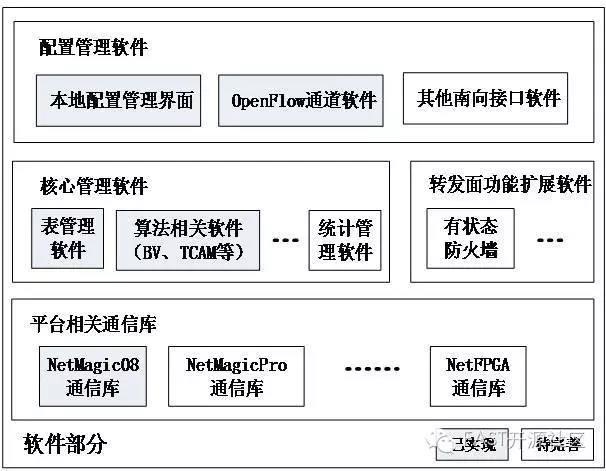

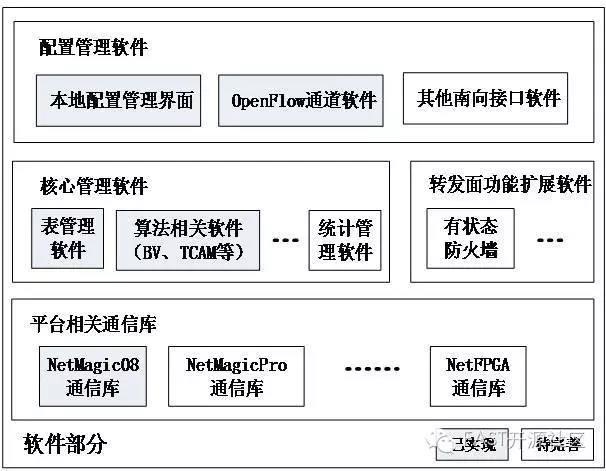

FAST软件由4部分组成,包括平台相关通信库,核心管理软件,转发面扩展软件以及配置管理软件。其中平台无关的核心管理软件,转发面扩展软件以及配置管理软件都是FAST用户可以修改的,统称为UA(User Application)。

平台相关通信库实现CPU软件与交换FPGA的通信,根据FPGA平台的不同,会采用不同的通信方式,例如与NetMagic08平台采用以太网方式进行通信,对于NetMagic Pro平台、NetFPGA平台则采用PCIe总线通信的方式。但平台相关软件与FPGA不同的通信方式对上层软件(核心管理软件、转发面功能扩展软件等)是透明的。即FAST项目定义了平台相关通信库对上层接口的规范,详见《FAST UA设计规范》。基于该规范开发的上层软件可不考虑下层的具体通信方式。

图2 FAST项目的软件架构

核心管理软件主要是SDN交换机数据平面中由CPU软件实现的基本功能,包括各种表管理软件,硬件相关的驱动和管理软件以及软硬件协同处理中的软件功能实现部分。各部分主要功能如下。

(1)表管理软件:负责所有控制器配置表格的维护,控制器flowmod命令对交换机表操作的命令主要由核心管理软件响应和实现。

(2)算法相关软件:是对硬件平台的驱动。例如NetMagic Pro平台硬件采用TCAM实现带掩码的查表,而NetMagic08平台采用SBV算法实现288位带掩码的查表。算法相关软件需要根据表管理软件要求,根据平台相关的算法实现特点,实现对硬件中流表的管理。

(3)统计管理软件:例如实现SDN交换机计数器的管理,将硬件实现的计数器(如流表项匹配分组数目计数器、端口接收计数器)和软件实现的计数器(流表项存活时间)进行统一的管理。又如数据平面实现的令牌桶参数、输出调度器配置的参数计算等。

配置管理软件主要实现SDN交换机的外部配置管理接口,包括SDN交换机需要的南向接口协议,如openflow协,以及本地的配置管理界面等。

4.基于FAST架构的用户开发

FAST是面向教学科研的开源项目,必须为网络技术研究和教学提供简单的第三方开发接口。根据不同科研单位的不同需求,这些开发接口分为多个层次。用户可以选择全定制功能开发模式,即基于平台提供的FPGA开发接口(UM接口)和软件开发接口(UA接口)开发自己的功能,优点是可以全新打造自己的功能,效率高,但难度较大,周期长,对开发人员的要求较高。FAST社区不推荐用户采用全定制功能开发的模式,而推荐采用用户定义功能模块开发模式。

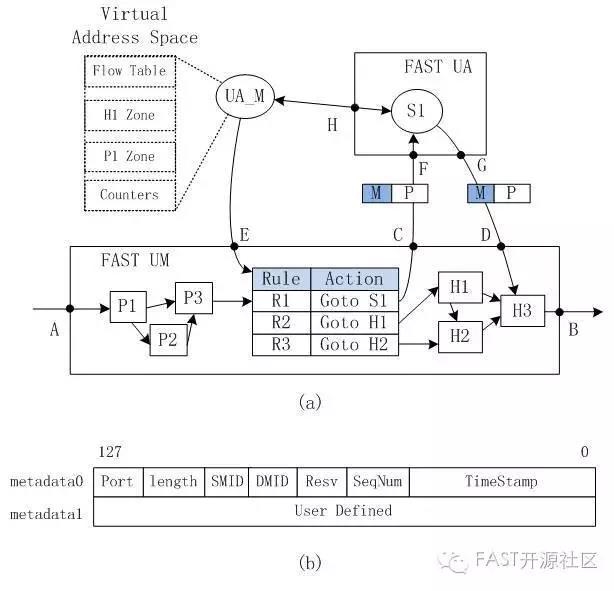

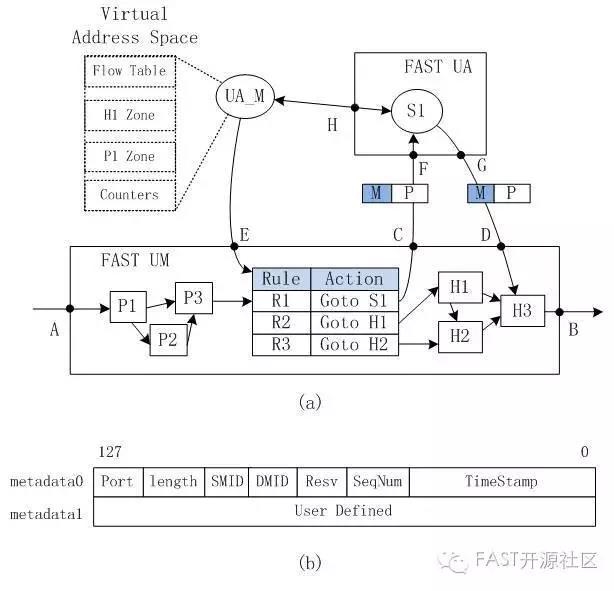

用户可借鉴已有的FAST软硬件架构和已有成熟的功能模块,只增加与自己应用相关的模块,优点是开发时间短,对人员要求较低,而且可以得到FAST社区最大程度的技术支持。用户可选择只开发自定义的硬件功能模块,或自定义的软件功能模块,或者同时开发硬件和软件模块,实现特定网络功能的协同处理,FAST用户定义模块开发示意如图3所示。

4.1 硬件UM开发

FAST社区已经开发了可工作的SDN转发的流水线demo程序,如图3所示。主要包含协议分析(Parser)、查表(match)以及动作执行(match)等阶段。用户可以在现有基础上增加自己的模块,如对新协议的parser模块(P4),新的动作执行模块(H4)等,而不需修改其他部分。FAST UM规范定义了5个接口,分别是A(从物理端口接收报文)、B(向物理接口发送报文)、C(将报文送软件处理)、D(从软件接收报文)和E(软件对硬件的配置接口)。

用户开发的硬件模块如果需要软件管理配置,只要将需要管理配置的寄存器、计数器和控制表等预先映射到虚拟地址空间中,软件UA按照虚拟空间的地址,通过平台提供的API可以直接访问到这些资源。虚拟地址空间的原理见《FAST虚拟地址空间设计和使用方法》。

4.2软件UA开发

用户可在CPU的用户空间进行定制模块的开发。用户程序通过平台提供的接口接收和发送数据包, 在每个数据包之前会携带32个字节的metadata,Metadata的定义和使用详见4.3节。

软件模块的开发主要遵循FAST UA规范中定义的F(接收Matadata和分组的接口)、G(发送Matadata和分组的接口)和H(向系统注册用户定义功能模块的接口,获取自己的MID号等),并将需要管理的硬件模块的资源在虚拟地址空间中定义。

根据图2中的软件架构,用户定义的模块位于SDN交换机数据平面,因此一方面可实现对L2-L3功能的软硬件协同处理,例如对新性网络协议的解析,另一方面也可实现数据平面对L4-L7处理功能的扩展,如扩展有状态防火墙功能,扩展对指定流的DPI功能等。

图3 用户定义功能模块开发原理示意图

(a)用户模块的工作原理(b)软硬件模块通信携带的metadata格式

4.3软硬件协同处理机制

FAST通过两种机制实现软硬件处理的协同。一是将软硬件处理模块统一编址,为每个action模块分配统一的MID(Module ID)。例如图3(a)中三个硬件action模块(H1、H2和H3)和一个软件功能模块(S1)都会分配一个唯一的MID。流表可以按照匹配结果将一个报文显示的分派到指定的软件或者硬件功能模块。二是软硬件分组通信时同时携带32字节的metadata。Metadata的定义如图3(b)所示。

FAST规范显式定义了Matadata的前16字节(Metadata0),如表1所示。通过Matadata,FPGA UM可将报文接收的端口、长度、接收的精确时间和序列号,以及发出的硬件模块,目的软件模块等信息送给软件,平台相关软件根据DMID信息将其送给指定的用户UA程序。用户UA程序处理完分组后,又可通过Metadata信息将其送给指定的硬件模块,也可直接指定目的输出接口(输出调度器也通过DMID指定)。

FAST没有对Matadata的后16字节(Metadata1)进行定义。当SMID和DMID都是用户自己设计时,可以自行约定Metadata1的含义,平台相关硬件和软件不对Metadata1进行任何检查和修改。

4.4 FAST.0参考设计

目前基于图1和图2的硬件和软件架构,以及图3的软硬件协同模型,国防科大课题组已经开发了支持openflow1.3的交换机原型FAST.0。FAST.0运行在NetMagic Pro平台,实现了与floodlight控制器的互联互通,以及标准的二层转发功能。

在FPGA硬件方面,FAST.0支持以太网/IPv4分组的解析,L2-L4层关键字的提取,以及基于比特向量算法(BV)的288位带掩码的规则匹配功能;在CPU软件方面,支持BV算法的管理,通用流表管理,标准的openflow 1.3的接口软件等。FAST.0软硬件代码已经完全开源,可作为用户基于FAST架构进行定制开发的基础。

5.基于FAST的创新研究示例

目前FAST项目基于NetMagic Pro等多个平台已经有支持openflow1.3的标准SDN交换机原型。基于这个原型,用户可以进一步增加自己的许多功能。本节通过两个例子说明基于FAST项目进行SDN交换机功能扩展研究的方法和流程。

在5.1的基于内容的转发机制ICN-X实现中,用户只需进行相关用户态软件开发,不需任何硬件编程;5.2实现的精准测量服务AMS(Accurate Measurement Service)中,需要分别设计软件和硬件模块,实现精确分组发送时刻控制以及时间戳标记。

5.1支持基于内容的转发机制(ICN-X)

用户可在FAST交换机上实现内容中心的转发机制ICN-X。这种机制在网络中可以与IPv4,IPv6转发机制共存。在FAST交换机上实现ICN-X转发机制的方法如下。

(1)将以太网type/length设置为“X”,用于指代上层协议为ICN-X;交换机可根据该域的值区别以太网帧封装的上层协议分组为IPv4,IPv6,ARP、MPLS或是ICN-X。

(2)在用户空间开发ICN-X协议转发软件ICN-X UA,ICN-X UA实现ICN-X的分组转发控制,ICN-X机制的路由和其他管理分组可通过ICN-X UA重新定向成Packet-in分组,发给控制器上相关的应用处理。

(3)ICN-A UA启动时向UA管理器(UA-M)注册,注册信息包括:

ICN-X UA的模块版本号/开发者信息;

ICN-X UA中需要控制器管理的流表(如由控制器APP计算的转发表等);

(4)UA-M给ICN-X UA分配唯一的模块号MID=Y;

(5)SDN控制器(应用)通过南向接口或其他方式获取ICN-X UA的模块号Y,以及需要通过FlowMod消息管理的流表信息;

(6)控制器(应用)根据Packet-in消息计算ICN-UA中转发规则,并通过flowMod消息配置这些规则;

(7)控制器(应用)产生并配置UM流表中的“钩子规则”,如:

Rule =“Type/length=X”,“other field= don’t care”

Atcion = Goto Module Y

经过上述步骤,用户定制的FAST交换机就可以在正常进行IP分组交换的同时,支持新的ICN-X交换机制了。ICN-X UA完成分组转发和二层封装后,直接将分组发送回FAST UM,同时在metadata中设置输出端口号以及输出调度器的MID。该分组会通过平台相关的软件和硬件送到UM的输出调度模块,不经修改的从相应的物理接口发出。

5.2支持精准测量服务(AMS)

主动测量是获取网络状态的有效手段。例如利用香港理工大学提出的oneProbe测试方法,通过在用户网中向分布在全球的web服务器发送背靠背的TCP分组对(packet pair),通过计算服务器对分组对得响应情况,精确的推断出用户主机到分布在全球的互联网服务器之间的带宽和延时情况,从而进一步推断广域网的链路特性。

这种测试的精确性取决于能否控制分组对真正的背靠背发送(中间没有插入延时),能否精确的获取分组对发出以及返回的时间戳。由于基于标准服务器的实现存在测量进程收到内核调度,中断处理以及系统时钟不精确等特点,很难保证测量的精确性,因此测量必须借助专用的,昂贵的可编程网卡实现,而且发送进程与网卡之间的时间和状态同步控制也比较复杂。

通过对部署在用户网络中的FAST交换机进行扩充,可以在交换机上方便的提供对精确的主动测量的支持。设发起测量的主机H连接FAST交换机端口A,连接被测网络的是FAST交换机的接口B,基本测量的流程为:测量主机H通过FAST接口A发送两个背靠背的TCP分组P1和P2,这两个分组经过交换机转发后从端口B发向被测网络;被测网络通过接口B返回对这两个分组的响应P1’和P2’,交换机将这两个分组通过接口A返回测试主机H。

通过对FAST交换机功能扩展,提供的精准测量服务包括:(1)交换机严格控制P1和P2从接口B背靠背发出,中间不插入任何延时;(2)交换机能够精确记录B口发出P1和P2,以及接收P1’和P2’的时间戳;(3)FAST交换机将时间戳信息通告给测试主机H。

要在FAST交换机上实现用户定义的精准测量服务,需要在FAST UM中开发专用的分组输出调度模块Hams,以及相关控制软件AMS UA。主机H使用FAST交换机扩展的AMS服务流程如下。

(1)控制器上AMS APP配置交换机的流表规则,将主机H与被测服务器S之间的测量报文(用H和S的地址标识,这些信息可通过离线方式或在线的方式通知控制器上的AMS APP),对送软件中的(预先完成向UA-M注册,并获取到MID)AMS UA模块处理;

(2)AMS UA将P1和P2两个报文标记为测量报文对,通过Matadata1中自定义的字段发给FAST UM中的Hams模块,Hams模块对输出调度器具有最高优先级,在收到两个报文后,通过输出调度模块背靠背发出,同时将发出时间记录在Hams模块中,在虚拟地址空间预先注册的寄存器中,AMS UA通过轮训读写该寄存器,获得报文发出的精确时间戳。

(3)P1’和P2’从B端口返回后,根据流表中的规则,会定向到AMS UA处理。AMS UA根据报文matadata0可获取分组到达的精确时间戳。

(4)控制器上AMS APP从南向接口获取主机H测量必须的分组对精确发出时间和响应的返回时间,并提交给主机H,完成AMS服务。

6.总结

综上所述,FAST技术架构具有以下特点。一是基于FPGA加多核CPU的异构处理平台设计,用户可以根据自己的特点通过软件编程或硬件编程实现自己定制的模块,进行交换功能的扩充;二是FAST平台采用开源结构,内部分组的处理流程完全可见;三是软硬件设计基于平台无关接口,不依赖特定的平台实现,可移植性好;四是具有完善的软硬件参考设计,研究人员可以根据自己研究的需求定制自己的交换机。

参考文献

(1)《FAST UM接口规范》

(2)《FAST UA设计规范》

(3)《FAST虚拟地址空间设计和使用方法》

(4)《FAST.0 硬件设计说明》

(5)《FAST.0 软件设计说明》

(以上文档整在修订,即将陆续发布。。。)