一、 应用背景

随着互联网技术的飞速发展,网络相关的软硬件应用也越来越多。但是应用的开发、测试大部分是在一些网络性能较好的局域网中进行的,但是现实中的网络是不可靠的,数据传输和交互可能存在丢包,乱序等问题,导致整个系统出现故障,因此模拟在广域网中存在的不确定问题,对应用的部署运行是必要的。

二、 方案概述

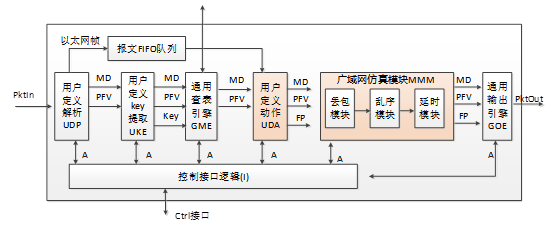

湖南新实自主研发的广域网硬件仿真平台,基于FPGA+CPU的FAST架构下实现,广域网仿真功能在硬件中实现,可模拟广域网中丢包,乱序,延时的情形。具体实现方式是在硬件中的五级流水线中插入广域网仿真模块。

三、 FAST五级流水线(FAST UM)

UM是FAST架构中硬件中最基础的模块,包含5个主要的子模块,可实现对网络分组的分组解析、查表匹配、动作转发,输出统计功能。

用户定义的解析(UDP)

根据用户特定的处理需求,解析分组的协议以及分组是否满足用户定制的属性分类,生成后续控制分组处理的分组特征向量(PFV)以及生成MD信息。

用户定义关键字提取(UKE)

根据分组的特征向量,提取分组查表得关键字并将查找关键字(Key)、PFV及MD送给GME模块。

通用查表引擎(GME)

根据产生的关键字查表,获取控制分组处理动作和输出控制的信息。

用户定义动作(UDA)

实现用户定义的对分组的特定处理,如修改分组头,分组分片与重组,添加二层分组头等。

通用输出引擎(GOE)

基于令牌桶实现对分组输出的整形,如限制发往特定CPU 软件UA或协议栈的流量,限制特定流发往特定端口的流量等。

四、 广域网仿真模块(MMM)

丢包模块

根据配置的丢包率对输入的包进行计数,即根据输入的百分比,将报文中的指定比例的包丢掉,如5%即在配置成效时将每接收到的100个报文中的前5个报文丢弃。

乱序模块

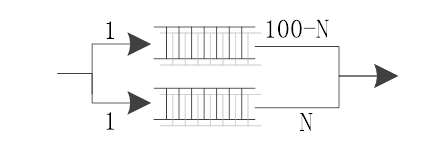

乱序模块是数据通过乒乓的方式存储在两个FIFO内。在输出时根据乱序的比例来实现对两个FIFO控制。

即输入时按1:1的方式将数据存储在两个FIFO中,在输出时则根据丢包比例进行乱序,即若乱序率为1%即输出时每输出99个数据后输出在对应FIFO多输出一个报文,即每个FIFO接2:2输出两个,以保证出现乱序。

延时模块

延时模块是对需要延时的数据在FIFO中进行缓存,直到达到延时确定的时间为止。即当第一个报文到达后开始记时,到指定时间输出数据报文。