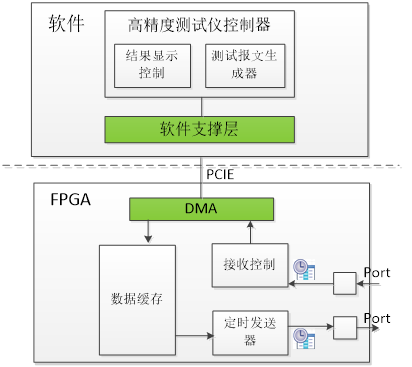

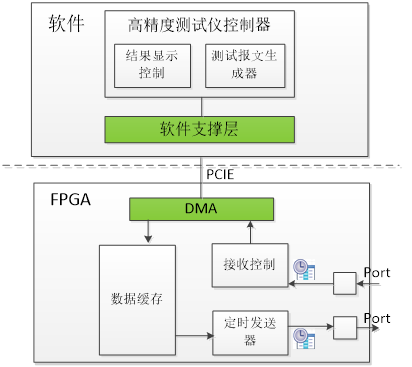

随着通信技术的快速发展,网络资源需求的增长以及高质量服务的诉求使的网络测量尤为重要,目前网络测试仪大多为国外产品且高精度测试仪价格昂贵。基于现状本方案设计了一种基于FPGA实现的高精度硬件测量解决方案,本方案通过主动测量的方式实现,其为针对网络延时进行测量,实现结构如图1所示。其分为软件与硬件实现部分,软件部分用于实现测试数据的下发以及测试结果显示功能。硬件包括数据缓存、接收控制、发送控制功能。在此方案中为了保证软硬件数据的交互,本方案提供了软件支撑层和DMA硬件支撑逻辑,同时为了确保测试的高精度,测试报文的时间戳使用硬件时间戳。

图1 硬件测量解决方案结构图

本方案中,通过软件测试报文生成器生成测试报文,通过软件支撑层下发给硬件存储,硬件可以支撑多个数据存储,并可以根据需求设置每个报文的发送间隔。发送时软件下发开始发送信号,则硬件根据软件配置的报文以及下发的次序,按时间发送间隔逐个进行发送。在发送时硬件记录发送第一个报文的时间戳值以及发送的报文个数。待发送结束后软件读取相应的时间戳和报文个数值。

在报文返回时,接收端记录接收的报文的达到时间戳值,并将接收的报文发送给软件。软件的结果显示模块根据接收的报文时间戳以及接收的报文个数与发送时间戳及发送的个数进行比较,从而可以分析出网络的发送延时以及网络的拥塞情况。

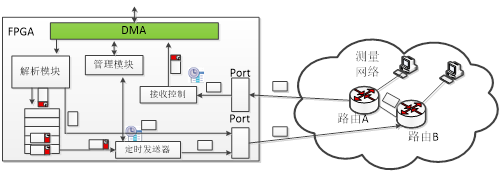

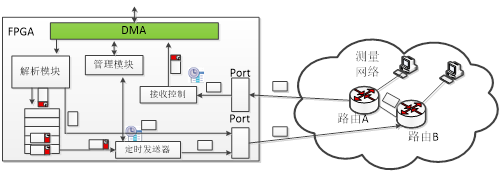

图2 硬件测量实现图

如图2 展示了硬件测量的实现的细节,本方案中硬件不仅支持测量报文的转发,同时也支持普通报文的处理。测量报文和普通报文由解析模块区分,当报文为普通报文时,则可以正常转发输出,当为测试报文时则进行缓存。软件下发每一个测量报文均携带一个MD信息,其中包含了当前报文相比前一个报文的发送间隔。定时发送器根据发送信号开始发送第一个报文,待发送结束后判断后续报文的发送间隔,根据间隔依次发送后续报文。发送过程中由定时发送器记录发送报文的个数,以及第一个发送报文的时间戳值。发送的测量报文经网络转发后将返回给测量模块。接收的测量报文会在接收控制器添加MD信息,即接收报文的硬件时间戳值。并将携带时间戳值得报文发送给软件进行计算处理。接收控制器会记录接收的测试报文的数量。收发的测试报文计数以及时间戳供软件进行分析网络情况时读取。

通过测试验证本测量方案可以实现纳秒级的测量精度,且可以实现延时的精度测试、网络拥塞情况测试以及网络传输延时变化测试。